Update on JEDEC Thermal Standards

Electronics Cooling

Focused on Thermal Management, TIMs, Fans, Heat Sinks, CFD Software, LEDs/Lighting

Facebook Google+ LinkedIn Twitter YouTube

googletag.cmd.push(function()

googletag.display('top-leaderboard');

);

Update on JEDEC Thermal Standards

September 17, 2012Electronics Cooling Number 3

The Role of Standards

The global electronics industry has for decades provided us with an astonishing array of products that have become essential to all aspects of modern life. Equally amazing is that they have done so in the context of a highly distributed supply chain model with hundreds of suppliers located all over the developed world. They are able to coordinate effectively, in part, because of industry standards that govern many aspects of component and system compatibility, safety and performance.

Because of the sensitivity of integrated circuit (IC) reliability and performance to temperature and the trend of increasing device power, thermal standards have grown in importance over time. Since its founding in 1990, the JEDEC JC-15 thermal standards committee has played a leading role in generating and promoting thermal characterization standards for semiconductor devices.

A Short History of IC Packaging

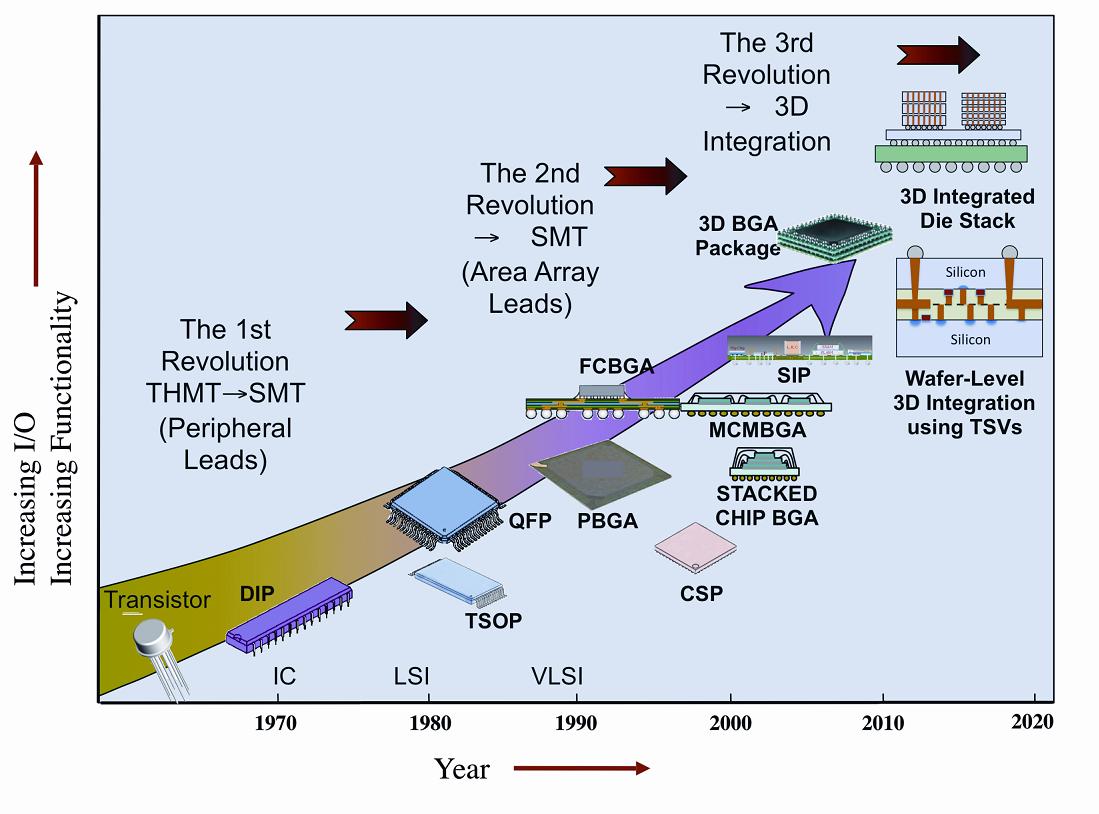

The standardization activities within JC-15 at a particular point in time reflect the trajectory of IC design and performance and the details of the associated packaging. It is useful to review this history as a prelude to the main discussion. The trajectory of package development is captured by the diagram in Figure 1 and is discussed below.

Leadframe Packages – Through-Hole Technology (THT)

Until the late 1980s, ICs were generally low in power and had small number of input/output (I/O) connections. The packaging technology of the day employed through-hole leads as illustrated by the DIP (dual in-line package) in the figure. The printed circuit boards (PCBs) of the time had a relatively small copper content and did not function very effectively as a heat-spreading fin.

Leadframe Packages – Surface Mount Technology (SMT)

In response to the greater IC complexity and leadcount, SMT was popularized in the late 1980s. The packaging technology was mostly leadframe based, with peripheral leads, as illustrated by the QFP (quad flat package) and TSOP (thin small-outline package) in the figure. Power had increased to a few watts. The greater number of package leads led to greater thermal coupling between the package and the PCB [1]. The PCB evolved to have internal copper planes, increasing its efficiency as a fin to assist the transport of heat into the surrounding air. The resultant die temperature in both testing and in the application depended critically on the details of the PCB construction.

Laminate Area Array Packages – Surface Mount Technology

In the mid-1990s, the peripheral SMT packages were soon followed by organic laminate substrate, area array packages such as the BGA (ball grid array). Initially, these were single-chip packages with a wire-bond electrical interconnect between the chip and the substrate.

Once the packaging industry was liberated from the electrical routing limitations of leadframe packages by the design flexibility of laminate substrates there was an explosion of new package types [2]:

- Multichip Packages using wire-bond interconnect

- Flip chip attach of chips (both single and multi) to substrate

- Stacking of chips with wire-bond interconnect between chips and to substrate

- 3D stacked laminate substrates

- System-in-package (SIP) multi-chip package with heterogeneous device types: ICs, memory chips, passive devices, analog chips, etc.

These package types led to even greater numbers of solder balls to accommodate the increased I/O requirements of many chips.

Thermal coupling to the PCB was often enhanced by way of solder balls routed to so-called “thermal vias” in the PCB, that served to efficiently transport heat from the package directly into the ground plane(s).

Area-array Leadframe Packages

Simultaneous with the development of laminate packages, advances in the etching of leadframes led to the capability for exposing small contact pads for each lead at the bottom surface of the package, eliminating the need for leads extending laterally from the package periphery. These are often referred to as leadless packages. The number of rows of lead pads range from one to as many as three or four.

Thermal coupling to the PCB was sometimes enhanced by displacing the die pad downward, making it flush to the bottom surface of the package, and allowing the pad to be soldered to pads connected to thermal vias routed to ground plane(s) of the PCB.

3-D Stacked Chips with Thru-Silicon-Via (TSV) Interchip Connection

In the quest to maintain Moore’s Law level scaling with respect to the number of transistors per chip even as the increase in the number of transistors per unit area was slowing down, the chip fab industry began a serious investment in making 3-D stacked chips [3]. There are a limited number of products on the market using this technology at present due to the still high cost of integrating the TSVs into stacks of thinned Si chips [4]. However, the investment by the industry is high and greater market penetration is expected. Among the package styles employing integrated 3-D chip stacks are:

- 3D integrated die stack packages

- Packages based on wafer-level 3-D integration

They are illustrated in the figure below.

Thermal Characterization Standards

Pre-1990

In the context of greater power levels and the introduction of SMT in the late 1980s, electronics companies were eager to adopt thermally-enhanced packages that were being developed. However, their task was made more difficult by the state of the thermal standards at that time. The existing standards lacked enough precision (particularly regarding the test boards) to enable a meaningful comparison of thermal performance of competing packages on the basis of the test data provided by the various semiconductor suppliers. Hence, the electronics companies were ultimately compelled to do their own thermal testing to be able to conduct this sort of comparison. This was a costly effort in terms of time and money.

It was this somewhat chaotic state of affairs in thermal test methodology that provided the motivation for the creation of the JC-15 committee within JEDEC in 1990.

JC-15 in the 1990s

At its founding, the charter of JC-15 was established as follows:

- To generate thermal measurement and modeling standards for microelectronic packaging.

- These standards shall be meaningful, consistent, and shall be proven to be scientifically sound.

- The standards will provide a common means of comparison of thermal phenomena for users of microelectronic packaging.

The second bulleted item represents a high standard for the committee to meet in the development of thermal standards. To this end, proposed standards are validated using testing and computer simulation, by individuals and in round-robin exercises. As an indication of the rigor of the ensuing analyses and test regimes, papers and articles based on them are often published by committee members after the completion of the work.

Since the inception of the committee, its member companies have included both semiconductor and packaging suppliers and computer and networking systems companies, along with thermal software and thermal test equipment vendors. This diversity has contributed to robust standards that take into account the concerns of all of the industries represented. In particular, the end-use environment for a component or material is always given due consideration in the development of the various standards.

Standards are proposed, developed, and published as a result of a “bottom up” process. They all begin with a member identifying a problem area in thermal characterization along with a concept for a standard that would ameliorate it. Before the lengthy process of turning a concept into a standard can begin, the initiative needs the endorsement of the committee and a champion to shepherd it along. There is often a core team or task group that make in-depth contributions to the development of the standard. Before a standard is finalized it needs to pass both committee and JEDEC Board of Directors ballots.

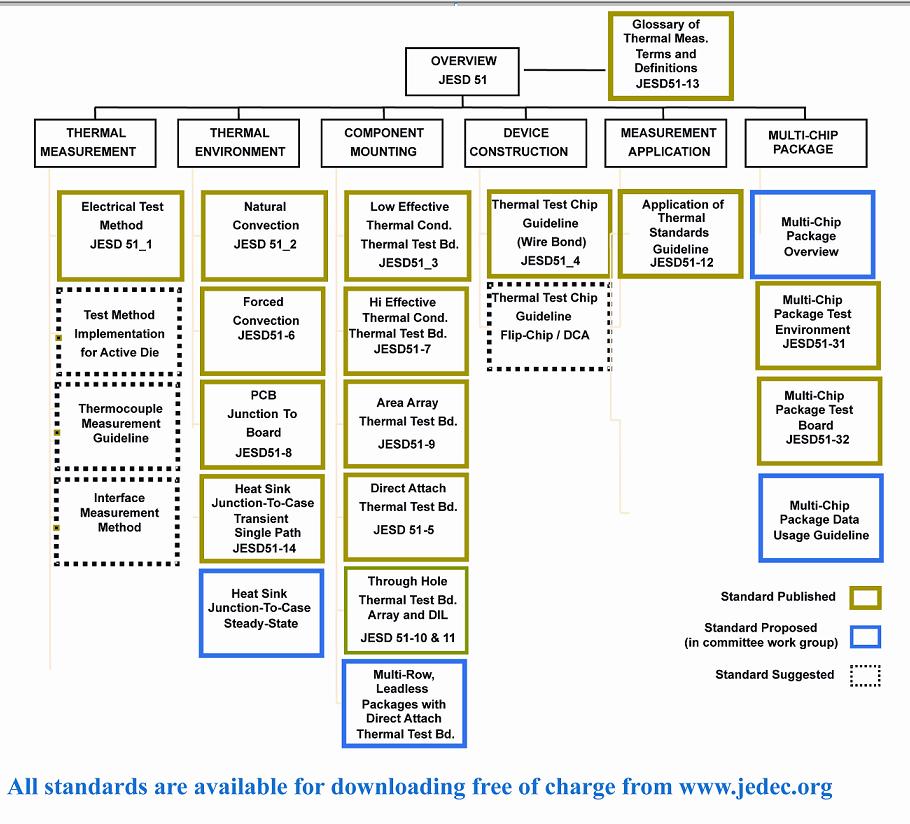

A modular framework was defined to help guide the development of test standards. Figure 2 illustrates this structure and lists the current single-chip package and multi-chip package standards along with those standards that are under active development or proposed.

The following bulleted items describe the various modules in the standards structure as well as those standards generated between 1990 and the end of 2001 [5, 6, 7].

- Thermal measurement method

- Electrical test method

- Thermal environment

- Natural convection chamber

- Forced air (i.e.: wind tunnel) [8]

- Junction-to-board thermal resistance cold plate [9, 10]

- Component mounting (i.e.: test board)

- Test boards for peripheral and area array SMT packages [11]

- Test boards for peripheral and area array THT packages

- Test board design extension to accommodate an exposed pad direct attach mechanism

- Device construction

- Wire bond test chip

The objective of the committee agenda in the 1990s was to provide a framework whereby different companies measuring the thermal performance of a given package using methods called out in the standards would have results differing by less than ± 10%. By all accounts, this was, indeed, what was accomplished. The end result is that when the semiconductor and package suppliers followed JEDEC thermal test standards, it was no longer necessary for electronics companies to duplicate their efforts and could make their package thermal performance comparison on the basis of the thermal data supplied by their suppliers.

Evolution of thermal metrics in single-chip packages

In 1990, the existing thermal metrics were the legacy thermal resistances, the junction-to-air thermal resistance (QJA) and the junction-to-case thermal resistance (QJC). Because of the greater power levels and reduced margin for error in predicting junction temperatures, QJA was no longer considered adequate for estimating the junction temperature in an actual application. It was relegated to its current role as enabling the ranking of competing packages in order of thermal performance.

Over the course of the 1990s, JC-15 created several new thermal metrics. The first, the junction-to-board thermal resistance (QJB) is useful in estimating the temperature difference between the junction temperature of an IC and that of the PCB at the center lead location of the package. As such, unlike QJA, it actually has some utility in estimating the junction temperature in an actual application when the board temperature is known and most of the heat dissipated in the package flows to the ambient air by way of the board. In the situation in which a fraction of the dissipated heat flows to the board, then the use of QJB provides a conservative estimate of the junction temperature.

The various “Theta” values are supplemented by “Psi” values, such as YJB and YJT. Unlike “Theta” values, that are measured in environments in which nearly 100% of the dissipated power flows from the junction to the indicated reference temperature location, the “Psi” values are measured in environments in which only a portion of the dissipated power flows to the indicated reference temperature location. The “Psi” values are not true thermal resistances and are referred to as Thermal Characterization Parameters. The “Psi” values can be of value in estimating the junction temperature in convection cooling environments in which there is no heat sink attached to the top of the package.

The following guideline is highly recommended in providing assistance in the interpretation and appropriate use of these metrics:

- JESD51-12 — Guidelines for Reporting and Using Electronic Package Thermal Information

JC-15 in 2001 and Beyond

The continued evolution of ICs in their power and I/O requirements and of packaging with its increasing complexity have led to new initiatives on the part of the committee.

Compact Thermal Models

The aforementioned single-parameter metrics may be of use in estimating the junction temperature based on temperature measurements in an actual system. However, they are not ideally suited for representing package thermal performance in a system-level thermal simulation. For this purpose, JC-15 has generated standards relating to the generation and application of compact thermal models (CTMs). In producing these standards, there was a significant contribution from European member companies who had participated in the DELPHI consortium [12, 13, 14].

The relevant standards are:

- JESD15: Thermal Modeling Overview

- JESD15-1: Compact Thermal Model Overview

- JESD15-3: Two-Resistor Compact Thermal Model Guideline

- JESD15-4: DELPHI Compact Thermal Model Guideline

- A fifth standard is currently working its way through the committee process: CTM Package Thermal Data (PTD) Interchange File Format (IFF). It is intended to enable the efficient transmission of CTM parameters from machine to machine.

Multichip Packages (MCPs)

A series of standards are devoted to the thermal testing of MCPs.

The Theta and Psi metrics are only appropriate for use in single-die packages. For MCPs, it is necessary to report the temperature difference measured between each chip and the reference temperature (TJ,i– TREF) along with its associated power (Pi), where the index, i, is a sequential number from 1 to N (the total number of chips), identifying each chip. One of the challenges in applying this methodology is that, in general, a particular power combination applied to the chips will produce a unique set of temperatures. In order to calculate the chip temperatures at combinations of power levels other than those used in the tests, the use of the Principle of Superposition is recommended [15].

- JESD51-31 — Thermal Test Environment Modifications for Multichip Packages

- JESD51-32 — Extension to JESD51 Thermal Test Board Standards to Accommodate Multi-chip Packages

- A guideline to aid in the interpretation of MCP thermal test data and the application of the Principle of Superposition for the purposed discussed above is in preparation.

Transient QJC Test

With increasing heat flux and total power in high-power devices and the use of high-conductivity solder thermal interface materials, traditional Theta, jc test methods using an embedded thermocouple in a cold plate are no longer adequate. The use of such a thermocouple leads to excessive errors in determining the case temperature. The transient test method enables the accurate determination of the case temperature without the use of an external thermocouple [16, 17. A software tool for performing the required calculations based on the raw test data is available for download at the JEDEC website along with the standard.

- JESD51-14 — Transient Dual Interface Test Method For The Measurement of the Junction-to-Case Thermal Resistance of Semiconductor Devices with Heat Flow through a Single Path

Lighting LEDs

High-power LEDs used for lighting purposes are becoming an ever more important class of semiconductors, due to their much greater energy efficiency than other lighting technologies. Until recently, the status of standards for their thermal characterization was in a condition similar to that for IC packages in the early 1990s [18]. The importance of accurate thermal characterization of lighting LEDs results from the fact that both the luminous output of the LED and its lifetime are significantly reduced when it is used at temperatures exceeding the recommended temperature range. The thermal characterization of lighting LEDs is further complicated by the fact that the luminous output must be measured in order to calculate the fraction of the total input power lost as heat [ 19]. The committee is coordinating with the European committee, CIE, in order to make use of their existing and evolving standards governing the measurement of the light output of LEDs. The LED standards published to date are:

- JESD51-50 — Overview of Methodologies for the Thermal Measurement of Single- and Multi-Chip, Single- and Multi-PN-Junction Light-Emitting Diodes (LEDs)

- JESD51-51 — Implementation of the Electrical Test Method for the Measurement of Real Thermal Resistance and Impedance of Light-Emitting Diodes with Exposed Cooling

- JESD51-52 — Guidelines for Combining CIE 127-2007 Total Flux Measurements with Thermal Measurements of LEDs with Exposed Cooling Surface

- JESD51-53 — Terms, Definitions and Units Glossary for LED Thermal Testing

On-chip Temperature Measurement

The continuing complexity of IC packages along with their high leadcounts make it increasingly difficult to continue the traditional practice of assembling a thermal test chip into a custom package and test it on a custom JEDEC-standard board. It is becoming more practical to depend on a thermal diode located on a application chip and to test it on the actual application board. There are obvious challenges in determining the peak die temperature from a measurement of a die-level temp sensor. The members of a task group within the committee are discussing the various tradeoffs in performing this sort of measurement.

Heat Sink Testing Standard Based on System Requirements

As mentioned in his editorial in this issue, Clemens Lasance introduced this topic at a recent meeting [20]. Hence, this effort is at a very early stage. We look forward to pursuing this issue further with him.

Conclusions

For over 20 years, the JEDEC JC-15 committee has been at the forefront of thermal standards activity in the global electronics industry. The nature of these activities has evolved over time consistent with the evolution of packaging toward greater complexity.

It is likely that, in the future, as packages continue to evolve into miniature sub-systems, the applicable standards will, by necessity, involve a tightly integrated combination of testing and modeling procedures in order to extract meaningful thermal performance data from packages under test. If the past is a guide to the future, the JC-15 committee will continue to meet these new challenges with standards based of the latest developments in thermal modeling and testing while reducing them to procedures that can be implemented in a manner suitable for the ever dynamic electronics industry.

Acknowledgement

This is to acknowledge the contributions of the many members of JC-15 too numerous to mention here, who, over the years, through their creativity, initiative, enthusiasm, and perseverance, have created such an enduring body of thermal standards for their industry.

References

- B. Guenin, “Packaging: Designing for Thermal Performance,” Electronics Cooling, Vol. 3, No. 2, May, 1997.

- B. Guenin, “The Many Flavors of BGA Packages,” ElectronicsCooling, Vol 8, No. 1, February, 2002.

- B. Guenin, “When Moore Is Less: Exploring the 3rd Dimension in IC Packaging,” ElectronicsCooling, Vol. 15, No. 1, February, 2009.

- An excellent resource in tracking the challenges facing the semiconductor and packaging industries along with 3D packaging developments is the website of the International Technology Roadmap for Semiconductors: http://www.itrs.net

- Note: all JEDEC standards are available for download at no cost at the JEDEC website: www.jedec.org.

- B. Guenin, “Component Thermal Characterization,” ElectronicsCooling, Vol. 7, No. 1, February, 2001.

- B. Guenin, “Thermal Standards for the 21st Century,” Proceedings, SEMI-THERM XVIII Conference, March, 2002..

- A. Claassen, B. Joiner, Z. Celik, and A. Ortega, “Development of the JEDEC Forced Convection Standard,” Proceedings, SEMI-THERM XVI Conference, March, 2000, pp.116-127.

- B. Joiner and V. Adams, “Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling,” Proceedings, SEMI-THERM XV Conference, March 1999, pp. 212-220.

- B. Joiner “Use of Junction-to-Board Thermal Resistance in Predictive Engineering,” Electronics Cooling, Vol. 5, No. 1, January, 1999.

- D. Edwards, “Development of JEDEC Standard Thermal Measurement Test Boards,” Proceedings, SEMI-THERM XII Conference, March, 1996, pp. 183-190.

- H. Rosten, C. Lasance, and J. Parry, “The World of Thermal Characterization According to DELPHI – Part I: Background to DELPHI,” IEEE Trans. CHMT, Vol. 20, 1997, pp. 384-391.

- Pape, H., and G. Noebauer, “Generation and Verification of Boundary Independent Compact Thermal Models for Active Components According to the DELPHI/SEED Methods,” ,” Proceedings, SEMI-THERM XV Conference, March, 1999, pp.201-211.

- S. Shidore, “Compact Thermal Modeling in Electronics Design” ElectronicsCooling, Vol. 13, No. 2, May, 2007

- B. Guenin, “Device Temperature Prediction in Multi-Chip Packages,” ElectronicsCooling, Vol. 12, No. 3, August 2006.

- D. Schweitzer, “Transient Dual Interface Measurement of the Rth-JC of Power Semiconductor Packages,” ElectronicsCooling, Vol. 16, No. 3, 2010.

- D. Schweitzer, H. Pape, L. Chen, R. Kutscherauer, and M. Walder, “Transient Dual Interface Measurement – A New JEDEC Standard for the Measurement of the Junction-to-Case Thermal Resistance,” Proceedings, SEMI-THERM XXVII Conference, March 20-24, 2011.

- C. Lasance and A. Poppe, “LED Thermal Standardization: A Hot Topic,” ElectronicsCooling, Vol. 15, No. 2, 2009.

- A. Poppe, B. Siegal, and G. Farkas, “Issues of Thermal Testing of AC LEDs,” Proceedings, SEMI-THERM XXVII Conference, March 20-24, 2011.

- C. Lasance, “Editorial: Every goodbye is the birth of a memory,” ElectronicsCooling, Vol. 18, No. 3, September, 2012.

About the Author

Electronics Cooling

Electronics Cooling magazine has been providing a technical data column since 1997 with the intent of providing you, the readers, with pertinent material properties for use in thermal analyses. We have largely covered the most common materials and their associated thermal properties used in electronics packaging.

« Previous Post

Thermal Facts & Fairy Tales: The Temperature Dependence of the Specific Heat

Next Post »

Editorial: Every Goodbye is the Birth of a Memory

Industry Sponsors

Click here to learn more about our Industry Sponsors!

googletag.cmd.push(function()

googletag.display('wrap-ad');

);

googletag.cmd.push(function()

googletag.display('bottom-leaderboard');

);

/* */

#simple-social-icons-2 ul li a, #simple-social-icons-2 ul li a:hover, #simple-social-icons-2 ul li a:focus background-color: #999999 !important; border-radius: 0px; color: #ffffff !important; border: 0px #ffffff solid !important; font-size: 16px; padding: 8px; #simple-social-icons-2 ul li a:hover, #simple-social-icons-2 ul li a:focus background-color: #666666 !important; border-color: #ffffff !important; color: #ffffff !important; #simple-social-icons-2 ul li a:focus outline: 1px dotted #666666 !important;

var fwtwoayeh4dyza2gje0l,fwtwoayeh4dyza2gje0l_poll=function()var r=0;return function(n,l)clearInterval(r),r=setInterval(n,l)();!function(e,t,n)document.documentElement).appendChild(o)(document,"script","omapi-script");

var mjwpiwlycniyrd52h3y5,mjwpiwlycniyrd52h3y5_poll=function()var r=0;return function(n,l)clearInterval(r),r=setInterval(n,l)();!function(e,t,n)(document,"script","omapi-script");

var h1nf9exkbtqxyscrutl1,h1nf9exkbtqxyscrutl1_poll=function()var r=0;return function(n,l)clearInterval(r),r=setInterval(n,l)();!function(e,t,n){if(e.getElementById(n))h1nf9exkbtqxyscrutl1_poll(function()if(window['om_loaded'])if(!h1nf9exkbtqxyscrutl1)h1nf9exkbtqxyscrutl1=new OptinMonsterApp();return h1nf9exkbtqxyscrutl1.init("u":"38891.701890","staging":0,"dev":0,"beta":0);,25);return;var d=false,o=e.createElement(t);o.id=n,o.src="https://a.optmnstr.com/app/js/api.min.js",o.async=true,o.onload=o.onreadystatechange=function()(document,"script","omapi-script");var fwtwoayeh4dyza2gje0l_shortcode = true;var mjwpiwlycniyrd52h3y5_shortcode = true;var pt2hu60kzfbem5hzf9fj_shortcode = true;var h1nf9exkbtqxyscrutl1_shortcode = true;

X

/* */

/* */

var omapi_localized = ajax: 'https://www.electronics-cooling.com/wp-admin/admin-ajax.php?optin-monster-ajax-route=1', nonce: '025a4db3e9', slugs: "fwtwoayeh4dyza2gje0l":"slug":"fwtwoayeh4dyza2gje0l","mailpoet":false,"mjwpiwlycniyrd52h3y5":"slug":"mjwpiwlycniyrd52h3y5","mailpoet":false,"pt2hu60kzfbem5hzf9fj":"slug":"pt2hu60kzfbem5hzf9fj","mailpoet":false,"h1nf9exkbtqxyscrutl1":"slug":"h1nf9exkbtqxyscrutl1","mailpoet":false ;